**PRODUCTION DATA SHEET**

#### **DESCRIPTION**

The LX1741 is a compact high operation is guaranteed at 1.6V input efficiency step-up boost controller. frequency modulation topology, the LX1741 was designed for maximum efficiency, reduced board size, and minimal cost.

Utilizing an external N-Channel MOSFET, the LX1741 designers maximum flexibility with respect to efficiency and cost. The LX1741 provides several design enhancements that improve overall performance under very light load currents by implementing control systems - thus providing a quiescent a shutdown current of less than 1µA.

The input voltage ranges from 1.6V to 6.0V, allowing for a wide selection of system battery voltages. Start-up

The output voltage is programmed Featuring a pseudo-hysteretic pulse easily using two external resistors in conjunction with the feedback pin. Depending on the MOSFET selected, the LX1741 is capable of achieving output voltages much higher than 40V.

The LX1741 has an additional feature offers for simple dynamic adjustment of the output voltage (i.e., up to  $\pm 15\%$  of the nominal output voltage). adjustment is achieved via an analog reference signal or a direct PWM input signal applied to the ADJ pin. Any PWM amplitude is easily accomcircuitry that is optimized for portable modated with a single external resistor.

The LX1741 is available in both the 8supply current of only 80µA (typ) and Pin MSOP, and the miniature 8-Pin MLP requiring minimal PCB area.

#### **KEY FEATURES**

- > 85% Maximum Efficiency

- 80µA Typical Quiescent Supply Current

- Externally Programmable Peak Inductor Current Limit For Maximum Efficiency

- Logic Controlled Shutdown

- < 0.5 µA Shutdown Current (typ)

- Dynamic Output Voltage Adjustment Via Analog Reference Or Direct PWM Input

- 8-Pin MSOP Package or 8-Pin MLP

#### APPLICATIONS/BENEFITS

- **Pagers**

- Wireless Phones

- **PDAs**

- Handheld Computers

- General LCD Bias Applications

- LED Driver

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com

| PACKAGE ORDER INFO  |                      |                          |  |  |  |

|---------------------|----------------------|--------------------------|--|--|--|

| T <sub>A</sub> (°C) | Plastic MLP<br>8-Pin | DU Plastic MSOP<br>8-Pin |  |  |  |

| 0 to 70             | LX1741CLM            | LX1741CDU                |  |  |  |

Note: Available in Tape & Reel. Append the letter "T" to the part number. (i.e. LX1741CDUT)

PRODUCTION DATA SHEET

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage ( $V_{CC}$ )<br>Feedback Input Voltage ( $V_{FB}$ ) |               |

|--------------------------------------------------------------------|---------------|

| Shutdown Input Voltage ( $V_{\overline{SHDN}}$ )                   |               |

| PWM Input Amplitude                                                |               |

| Analog Adjust Input Voltage (V <sub>ADJ</sub> )                    |               |

| Source Input Current (I <sub>SRC</sub> )                           |               |

| Operating Junction Temperature                                     | 150°C         |

| Storage Temperature Range                                          | 65°C to 150°C |

| Lead Temperature (Soldering 180 seconds)                           | 235°C         |

|                                                                    |               |

Note: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of specified terminal.

#### THERMAL DATA

#### **DU** Plastic MSOP 8-Pin

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $	heta_{JA}$      | 206°C/W |

|-----------------------------------------------------------|---------|

| THERMAL RESISTANCE-JUNCTION TO CASE, $\theta_{\text{JC}}$ | 39°C/W  |

### LM Plastic MLP 8-Pin

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{\text{JA}}$ | 41°C/W  |

|--------------------------------------------------------------|---------|

| THERMAL RESISTANCE-JUNCTION TO CASE, $\theta_{JC}$           | 5.2°C/W |

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JC})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

| PACKAGE PIN OUT          |   |   |      |  |  |  |  |  |

|--------------------------|---|---|------|--|--|--|--|--|

|                          |   |   |      |  |  |  |  |  |

| SRC                      | 1 | 8 | NDRV |  |  |  |  |  |

| GND                      | 2 | 7 | IN   |  |  |  |  |  |

| CS                       | 3 | 6 | FB   |  |  |  |  |  |

| ADJ 🔃                    | 4 | 5 | SHDN |  |  |  |  |  |

| DU PACKAGE<br>(Top View) |   |   |      |  |  |  |  |  |

|                          |   |   | 1    |  |  |  |  |  |

| SRC                      | 1 | 8 | NDRV |  |  |  |  |  |

| GND                      | 2 | 7 | IN   |  |  |  |  |  |

| cs                       | 3 | 6 | FB   |  |  |  |  |  |

| ADJ                      | 4 | 5 | SHDN |  |  |  |  |  |

| LM PACKAGE<br>(Top View) |   |   |      |  |  |  |  |  |

| NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IN   | Unregulated IC Supply Voltage Input – Input range from +1.6V to 6.0V. Bypass with a 1μF or greater capacitor for operation below 2.0V.                                                                                                                                                                                                             |  |  |  |  |

| FB   | Feedback Input – Connect to a resistive divider network between the output and GND to set the voltage at V <sub>FB</sub> (see Output Voltage Programming: Application Information).                                                                                                                                                                |  |  |  |  |

| SHDN | Active-Low Shutdown Input – A logic low shuts down the device and reduces the supply current to 0.1μA. Connect SHDN to V <sub>CC</sub> for normal operation.                                                                                                                                                                                       |  |  |  |  |

| NDRV | MOSFET Gate Driver – Connects to an external N-Channel MOSFET.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| CS   | Current-Sense Amplifier Input – Connecting a resistor between CS and GND sets the peak inductor current limit.                                                                                                                                                                                                                                     |  |  |  |  |

| GND  | Common terminal for ground reference.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ADJ  | An applied PWM Signal Input becomes the internal reference, via an internal filter and gain resistor, thus allowing for a dynamic output voltage adjustment of $\pm 15\%$ (i.e., corresponding to the duty cycle variance). Connecting this pin to ground causes the device to revert to the internal voltage reference (note: refer to figure 8). |  |  |  |  |

| SRC  | MOSFET Current Sense Input - Connects to the External N-Channel MOSFET Source.                                                                                                                                                                                                                                                                     |  |  |  |  |

PRODUCTION DATA SHEET

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature  $0^{\circ}\text{C} \leq T_{A} \leq 70^{\circ}\text{C}$  except where otherwise noted and the following test conditions:  $V_{IN} = 3V$ ,  $V_{OUT} = 18.5V$ ,  $V_{ADJ} = 0V$ ,  $R_{LOAD} = 9.25k\Omega$ ,  $\overline{SHDN} = V_{IN}$

| Parameter                                | Symbol                  | Test Conditions            |       | LX1741 |                            |                  |

|------------------------------------------|-------------------------|----------------------------|-------|--------|----------------------------|------------------|

| Farameter                                | Syllibol                | rest conditions            | Min   | Тур    | Max                        | Units            |

| Operating Voltage                        | V <sub>IN</sub>         |                            | 1.6   |        | 6.0                        | V                |

| Minimum Start-up Voltage                 | V <sub>SU</sub>         | T <sub>A</sub> = +25°C     |       |        | 1.6                        | V                |

| Start-up Voltage Temperature Coefficient | <b>k</b> <sub>VST</sub> |                            |       | -2     |                            | mV/°C            |

| Ovices and Oversent                      |                         | V <sub>FB</sub> = 1.5V     |       | 80     | 100                        | μΑ               |

| Quiescent Current                        | IQ                      | V <sub>SHDN</sub> < 0.4V   |       | 0.2    | 0.5                        | μА               |

| FB Threshold Voltage                     | $V_{FB}$                | $V_{ADJ} = GND$            | 1.264 | 1.290  | 1.316                      | ·V               |

| FB Input Bias Current                    | I <sub>FB</sub>         | V <sub>FB</sub> = 1.4V     | -200  |        | 200                        | nA               |

| ADJ Input Voltage Range <sup>1</sup>     | $V_{ADJ}$               |                            | 0     |        | V <sub>IN</sub> –<br>100mV | ٧                |

| ADJ Input Bias Current                   | I <sub>ADJ</sub>        | $V_{ADJ} = V_{FB} = 1.29V$ | 0.3   |        | 1.0                        | μΑ               |

| SRC Input Current                        | I <sub>SRC</sub>        |                            |       |        | 8.0                        | A <sub>RMS</sub> |

| Shutdown Input Bias Current              | I <sub>SHDN</sub>       | SHDN = GND                 | -50   |        | 50                         | nA               |

| Shutdown High Input Voltage              | $V_{\overline{SHDN}}$   | V <sub>IN</sub> = 2V       | 1.6   |        |                            | V                |

| Shutdown Low Input Voltage               | V <sub>SHDN</sub>       | V <sub>IN</sub> = 2V       |       |        | 0.4                        | V                |

| Current Sense Bias Current               | Ics                     |                            | 3.0   | 5.0    | 7.0                        | μА               |

| Minimum Peak Current                     | I <sub>MIN</sub>        | GBNT 2                     |       | 145    |                            | mA               |

| Comparator A Delay                       | t <sub>D</sub>          | GBNT <sup>2</sup>          |       | 620    |                            | ns               |

| NDRV Sink Current                        | I <sub>SNK</sub>        | V <sub>IN</sub> = 5V       | 50    |        |                            | mA               |

| NDRV Source Current                      | I <sub>SRC</sub>        | V <sub>IN</sub> = 5V       | 100   |        |                            | mA               |

| Minimum Off-Time                         | t <sub>OFF</sub>        | $V_{FB} = 1V$              | 100   |        | 500                        | ns               |

#### Notes:

- When using a DC source to adjust V<sub>OUT</sub>, the recommended V<sub>ADJ</sub> (range) is from 0.9V to 1.50V: see figure 3 and 8.

Guaranteed typical value (not tested) @ T<sub>A</sub> = 25°C (see section "Inductor Selection and Current Limit Programming")

PRODUCTION DATA SHEET

#### APPLICATION CIRCUITS

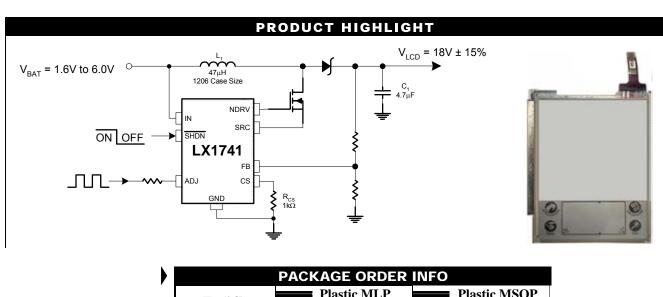

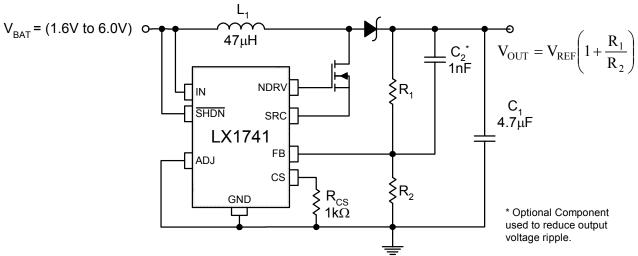

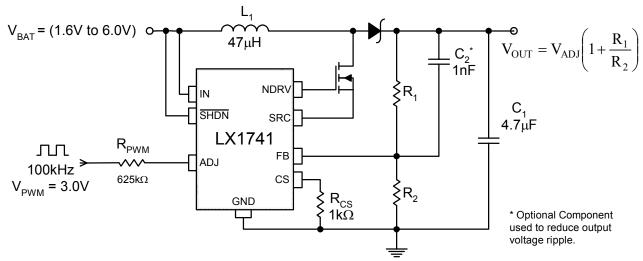

#### **Typical LCD Bias Applications**

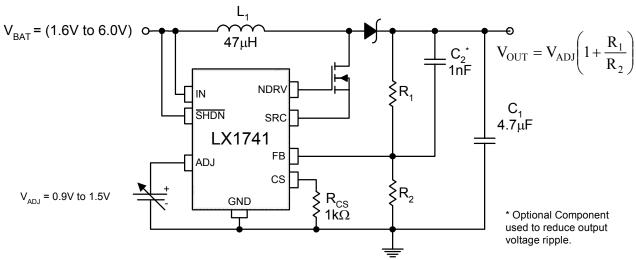

Figure 1 – Fixed Output Voltage Operation

Figure 2 – Dynamic Output Voltage Operation Via PWM Input

**Note**: An in-series  $R_{PWM}$  will attenuate the PWM amplitude to the proper signal level at the ADJ pin. With the  $R_{PWM}$  value shown, a PWM signal having a duty of 30% to 50% will generate 0.9V to 1.5V at the ADJ pin.

PRODUCTION DATA SHEET

#### **APPLICATION CIRCUITS (CONTINUED)**

#### **Typical LCD Bias Applications (Cont)**

Figure 3 – Dynamic Output Voltage Operation Via Analog Voltage Input

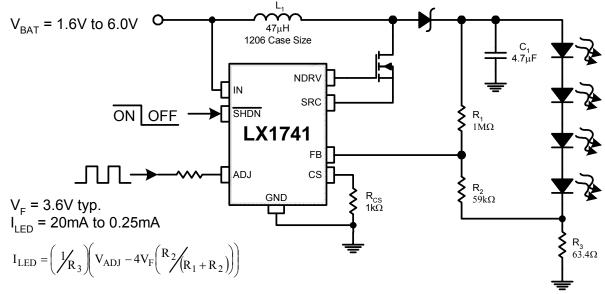

#### **LED Driver Application**

Figure 4 – LED Driver with Full-Range Dimming Via PWM Input

**Note** The component values shown are only examples for a working system. Actual values will vary greatly depending on desired parameters, efficiency, and layout constraints.

PRODUCTION DATA SHEET

# Vbat = 3.2V Vout = 40V Vout = 40V Res 20K Res 20K

Figure 5 - Application of Fixed Output, 40V @ 20mA

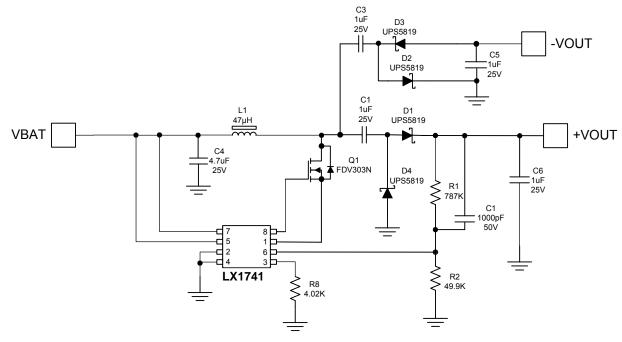

Figure 6 - Application of Dual Output, ± 20V @ 2mA

PRODUCTION DATA SHEET

#### APPLICATION INFORMATION

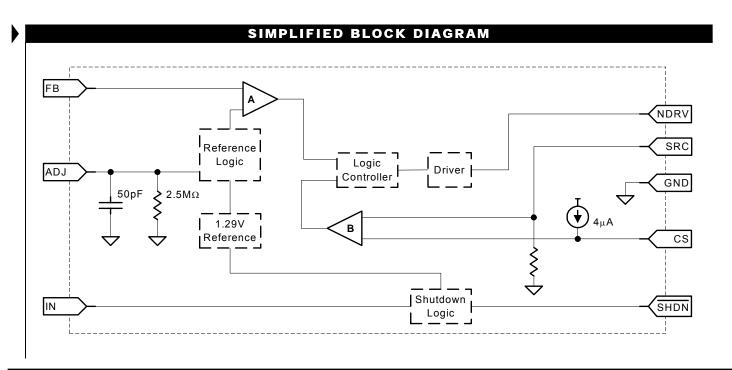

#### **FUNCTIONAL DESCRIPTION**

The LX1741 is a Pulse Frequency Modulated (PFM) boost converter that is optimized for large step up voltage applications like LCD biasing. It operates in a pseudohysteretic mode with a fixed switch "off time" of 300ns. Converter switching is enabled when the feedback voltage,  $V_{\rm FB}$ , falls below the 1.29V reference or VADJ (see Block Diagram). When this occurs, comparator A activates the off-time controller. The off-time controller and the current limiter circuit activate comparator B which toggles the NDRV output circuit. The NDRV output is switched "on" (and remains "on") until the inductor current ramps up to the peak current level. This current level is set via the external  $R_{\rm CS}$  resistor and monitored through the CS and SRC inputs.

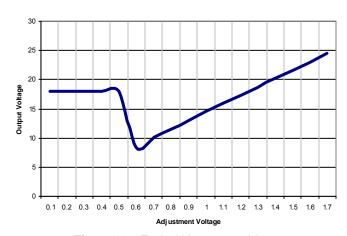

The load is powered from energy stored in the output capacitor during the inductor charging cycle. Once the peak inductor current value is achieved, the NDRV output is turned off (off-time is typically 300ns) allowing a portion of the energy stored in the inductor to be delivered to the load. This causes the output voltage to continue to rise at the input to the feedback circuit (i.e., comparator A). If the voltage at the FB input is still less than 1.29V at the end of the off-time period, the NDRV output switches the external FET "on" and the inductor charging cycle repeats until  $V_{\rm FB}$  is greater than the internal reference. This switching behavior is shown in Figure 9 and 11.

The application of an external voltage source at the ADJ pin allows for output voltage adjustment over a typical range of approximately  $\pm 15\%$ . The designer can select one of two possible methods. One option is to vary the reference voltage directly at the ADJ pin by applying a DC voltage from 0.9 to 1.5V. The second option is to connect a PWM logic signal to the ADJ pin (e.g., see Figure 2). The LX1741 includes an internal 50pF capacitor to ground that works with an external resistor to create a low-pass filter (i.e., filter out the AC component of a pulse width modulated input of  $f_{PWM} \ge 100 \text{KHz}$ ).

The adjustment voltage level is selectable (with limited accuracy) by implementing the voltage divider created between the external series resistor and the internal  $2.5M\Omega$  resistor. If the DC voltage at the ADJ pin drops below 0.6V, the device will revert to the internal reference voltage level of 1.29V. A typical adjustment curve is shown in Figure 8 (see section titled: Characteristic Curves). Disabling the LX1741 is achieved by driving the SHDN pin with a low-level logic signal thus reducing the device power consumption to less than  $1\mu A$ .

#### **OUTPUT VOLTAGE PROGRAMMING**

Selecting the appropriate values for R1 and R2 in the voltage divider connected to the feedback pin programs the output voltage. Using a value of 49.9K for R2 works well in most applications. R1 can be determined by the following equation (where  $V_{REF} = 1.29V$  nominal):

$$R1 = R2 \times \frac{\left(V_{OUT} - V_{REF}\right)}{V_{REF}}$$

DESIGN EXAMPLE:

Let R2 equals 49.9K and the required VOUT equal to 18V.

$$R1 = 49.9K\Omega \times \frac{(18V - 1.29V)}{1.29V} = 646.4K\Omega$$

# INDUCTOR SELECTION AND CURRENT LIMIT PROGRAMMING

Setting the level of peak inductor current to, at least, 1.5x the expected maximum DC input current will minimize the inductor size, the input ripple current, and the output ripple voltage. The designer is encouraged to use inductors that will not saturate at the peak inductor current level. An inductor value of  $47\mu H$  is recommended. Choosing a lower value emphasizes peak current overshoot while choosing a higher value emphasizes output ripple voltage. The peak switch current is defined using a resistor placed between the CS terminal and ground and the  $I_{PEAK}$  equation is:

$$I_{_{PEAK}} = I_{_{MIN}} + \begin{bmatrix} V_{_{IN}} \\ \end{bmatrix} t_{_{D}} + \begin{bmatrix} I_{_{SCALE}} \end{bmatrix} R_{_{CS}}$$

The maximum  $I_{PEAK}$  value is limited by the  $I_{SRC}$  value (max. =  $0.8A_{RMS}$ ). The minimum  $I_{PEAK}$  value is defined when  $R_{CS}$  is zero. A typical value for the minimum peak current ( $I_{MIN}$ ) at 25°C is 145mA. The parameter  $t_D$  is related to internal operation of comparator A. A typical value at 25°C is 620ns. A typical value of  $I_{SCALE}$  at 25°C is 31mA per  $K\Omega$ . All of these parameters have an effect on the final  $I_{PEAK}$  value.

#### DESIGN EXAMPLE:

Determine  $I_{PEAK}$  where  $V_{IN}$  equals 3.0V and  $R_{CS}$  equals 4.02K $\Omega$  using nominal values for all other parameters.

$$I_{PEAK} = 145 \text{mA} + \left(3.0 \frac{1}{47} \frac{1}{\mu H}\right) \times 620 \text{ns} + \left(31 \frac{1}{47} \frac{1}{\mu H}\right) \times 4.02 \text{K}\Omega$$

The result of this example yields a nominal  $I_{PEAK}$  equal to 145mA + 39.6mA + 124.6ma = 309.2mA.

**PRODUCTION DATA SHEET**

#### **APPLICATION INFORMATION (CONTINUED)**

#### **OUTPUT RIPPLE CAPACITOR SELECTION**

Output voltage ripple is a function of the inductor value (L), the output capacitor value ( $C_{OUT}$ ), the peak switch current setting ( $I_{PEAK}$ ), the load current ( $I_{OUT}$ ), the input voltage ( $V_{IN}$ ) and the output voltage ( $V_{OUT}$ ) for a this boost converter regulation scheme. When the switch is first turned on, the peak-to-peak voltage ripple is a function of the output droop (as the inductor current charges to  $I_{PEAK}$ ), the feedback transition error (i.e., typically 10mV), and the output overshoot (when the stored energy in the inductor is delivered to the load at the end of the charging cycle). Therefore the total ripple voltage is

$$V_{RIPPLE} = \Delta V_{DROOP} + \Delta V_{OVERSHOOT} + 10 \text{mV}$$

The initial droop can be estimated as follows where the 0.5v value in the denominator is an estimate of the voltage drop across the inductor and the FET's  $R_{DS\ ON}$ :

$$\Delta V_{DROOP} = \frac{\left(\frac{L}{C_{OUT}}\right) \times \left(I_{PK} \times I_{OUT}\right)}{\left(V_{IN} - 0.5\right)}$$

The output overshoot can be estimated as follows where the 0.5 value in the denominator is an estimate of the voltage drop across the diode:

$$\Delta V_{\text{OVERSHOOT}} = \frac{\frac{1}{2} \times \left(\frac{L}{C_{\text{OUT}}}\right) \times \left(I_{PK} - I_{\text{OUT}}\right)^{2}}{\left(V_{\text{OUT}} + 0.5 - V_{\text{IN}}\right)}$$

DESIGN EXAMPLE:

Determine the  $V_{RIPPLE}$  where  $I_{PK}$  equals 200mA,  $I_{OUT}$  equals 35mA, L equals 47 $\mu$ H,  $C_{OUT}$  equals 4.7 $\mu$ F,  $V_{IN}$  equals 3.0V, and  $V_{OUT}$  equals 18.0V:

$$\Delta V_{DROOP} = \frac{\binom{47\mu H}{4.7\mu F} \times (200\text{mA} \times 35\text{mA})}{(3.0 - 0.5)} = 28\text{mV}$$

$$\Delta V_{OVERSHOOT} = \frac{\frac{1/2}{2} \times \left(\frac{47 \mu H}{4.7 \mu F}\right) \times \left(200 mA - 35 mA\right)^2}{\left(18.0 + 0.5 - 3.0\right)} = 9.4 mV$$

Therefore, for  $C_{OUT}$  equals 4.7 $\mu$ F:

$$V_{RIPPLE} = 28mV + 9.4mV + 10mV = 47.4mV$$

Increasing the output capacitor value results in the reduction of the output voltage ripple voltage. Low ESR capacitors are recommended to reduce ripple caused by the switching current. Multi-layer ceramic capacitors with X5R or X7R dielectric are a superior choice featuring small size, very low ESR, and a temperature stable dielectric. Low ESR electrolytic capacitors such as solid tantalum or OS-CON types are also acceptable. Moreover, adding a capacitor from the output to the feedback pin (C2) allows the internal feedback circuitry to respond faster which further minimizes output voltage ripple and reduces noise coupling into the high impedance feedback input.

#### **DIODE SELECTION**

A Schottky diode is recommended for most applications (e.g. Microsemi UPS5819). The low forward voltage drop and fast recovery time associated with this device supports the switching demands associated with this circuit topology. The designer is encouraged to consider the diode's average and peak current ratings with respect to the application's output and peak inductor current requirements. Further, the diode's reverse breakdown voltage characteristic must be capable of withstanding a negative voltage transition that is greater than  $V_{\rm OUT}.\,$

#### TRANSISTOR SELECTION

The LX1741 can drive up to 100mA of gate drive current. An N-channel MOSFET with a relatively low threshold voltage, low gate charge and low  $R_{\rm DS(ON)}$  is required to optimize overall circuit performance. The LXE1741 Evaluation Board uses a Fairchild FDV303. This NMOS device was chosen because it demonstrates an  $R_{\rm DS~ON}$  of  $0.33\Omega$  and a total gate charge  $Q_{\rm g}$  of 1.64nC (typ.).

#### PCB LAYOUT

The LX1741 produces high slew-rate voltage and current waveforms hence; the designer should take this into consideration when laying out the circuit. Minimizing trace lengths from the IC to the inductor, transistor, diode, input and output capacitors, and feedback connection (i.e., pin 6) are typical considerations. Moreover, the designer should maximize the DC input and output trace widths to accommodate peak current levels associated with this circuit.

PRODUCTION DATA SHEET

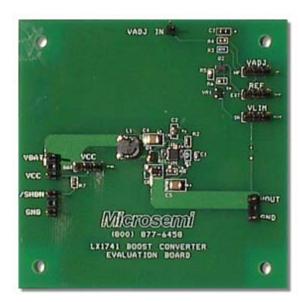

#### **EVALUATION BOARD**

#### **OVERVIEW**

The LXE1741 evaluation board is available from *Microsemi* for assessing overall circuit performance. The evaluation board, shown in Figure 5, is 3 by 3 inches (i.e., 7.6 X 7.6cm) square and factory calibrated to provide a nominal 18V output from a 1.6V to 6.0V input. Circuit designers can easily modify output voltage and current to suit their particular application by replacing the R1 and  $R_{\rm CS}$  values respectively. Moreover, inductor, FET, and diodes are easily swapped out to promote design verification of a circuit that maximizes efficiency and minimizes cost for any particular application. The input and output connections are described in Table 1.

#### **ELECTRICAL CONNECTIONS**

Apply the DC input voltage to VBAT (*not VCC*) however, the LX1741 IC may be driven from a separate DC source via the VCC input (if desired). Connect the test load to VOUT. Primary output voltage adjustment is accomplished by selecting the appropriate value for R1. Optional fine adjustment of the output voltage is achieved by applying either a DC voltage or a PWM-type signal to the VADJ input. Both low frequency (f < 100 KHz) and high frequency (f > 100 KHz) PWM signals are accommodated by choosing the appropriate jumper connection. Further, the VADJ circuit can be bypassed by selecting the appropriate jumper position (see Table 2).

The LX1741 exhibits a low quiescent current ( $I_Q < 1\mu A$ : typ) during shutdown mode. The SHDN pin can be used to examine shutdown performance on the evaluation board. This pin is pulled-up to VCC via a  $10 \mathrm{K}\Omega$  resistor. Grounding the SHDN pin shuts down the IC however, the load is still capable of drawing current through the inductor & diode circuit path. Hence,  $V_{OUT}$  during shutdown will be approximately  $V_{BAT}$  minus the inductor and diode forward voltage drop.

The LX1741 can achieve output voltages in excess of 25V. In certain applications, it is necessary to protect the load from excessive voltage excursions. The evaluation board provides a VLIM jumper position for this purpose. Engaging this jumper position ensures that the output voltage does not exceed 25V.

The LXE1741 evaluation board provides an easy and cost effective solution for evaluation on the LX1741. The factory installed component list for the evaluation board is provided in Table 3 and the schematic is shown in Figure 6.

Figure 7 - LX1741 Circuit Evaluation Board

**Table 1: Input and Output Pin Assignments**

| Pin<br>Name | Allowable<br>Range                                                                                                                             | Description                                                              |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| VBAT        | 0 to 6V Main power supply for output. (Set external current limit to 0.5A)                                                                     |                                                                          |  |  |

| VCC         | LX1741 power. May be strapped to VBAT or use a separate supply if VCC jumper is in the SEP position. Do not power output from VCC pin on board |                                                                          |  |  |

| SHDN        | 0 to VCC                                                                                                                                       | Pulled up to VCC on board (10K $\Omega$ ), Ground to inhibit the LX1741. |  |  |

| VOUT        | VCC to 25V                                                                                                                                     | Programmed for 18V output, adjustable up to 25V.                         |  |  |

| VADJ IN     | 0 to VCC                                                                                                                                       | Apply a DC input or PWM input to adjust the output voltage.              |  |  |

Note: All pins are referenced to ground.

PRODUCTION DATA SHEET

#### **EVALUATION BOARD (CONTINUED)**

**Table 2: Jumper Pin Position Assignments**

| Jumper / Position | Function                                                                                                                                                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC/ VBAT         | Use this position when powering VBAT and VCC from the same supply. Do not connect power to the VCC input when using this jumper position.                             |

| VCC/ SEP          | Use this position when using a separate VCC supply (different from VBAT).                                                                                             |

| REF/ EXT          | Use this position when using an external source to adjust the output voltage.                                                                                         |

| REF/ INT          | Use this position when using the fixed output voltage mode. In this mode the output voltage can be varied by changing the value of R1 as described in the data sheet. |

| ADJ/ HF           | Use this position when adjusting the output with an external PWM that has a repetition rate in excess of 100KHz.                                                      |

| ADJ/ LF           | Use this position when adjusting the output with an external PWM that has a repetition rate less than 100KHz. Or when using a DC adjustment voltage.                  |

| VLIM/ IN          | Use this position when adjusting the output voltage to prevent the output voltage from accidentally exceeding 25V.                                                    |

| VLIM/ OUT         | This position disables the output voltage adjustment clamp. This position may be desired if maximizing efficiency when operating near 25V output level.               |

Note: Always put jumpers in one of the two possible positions

Table 3: Factory Installed Component List for the LX1741Evaluation Board

| Ref   | Description                             | Supplier    | Part Number     |

|-------|-----------------------------------------|-------------|-----------------|

| C1    | CAPACITOR, COG, 1000pF, 0402, 50V       | MURATA      | GRM36X7R102M050 |

| C2    | CAPACITOR, X7R, 0.1uF, 0805, 50V        | MURATA      | GRM40X7R104M050 |

| C3    | CAPACITOR, Y5V, 2.2uF, 0805, 16V        | AVX         | 0805YG225ZAT    |

| C4,5  | CAPACITOR, X5R, 4.7uF, 1210, 25V        | TAIYO YUDEN | CETMK325BJ475MN |

| CR1   | RECTIFIER, SCHOTTKY, 1A, 40V, POWERMITE | MICROSEMI   | UPS5819         |

| L1    | INDUCTOR, 47UH, 480mA, SMT              | TOKO        | A920CY-470M     |

| JP1-7 | 3 TERM HEADER, 0.1 IN CTR               | 3M          | 929647-09-36-I  |

| SB1-4 | JUMPER                                  | 3M          | 929955-06       |

| Q1    | MOSFET, N-CHAN, 25V, SOT-23             | FAIRCHILD   | FDV303N         |

| Q2    | TRANSISTOR, NPN, 40V, SOT-23            | ON          | MMBT3904LT1     |

| R1    | RESISTOR, 698K, 1/16W, 0603             | PANASONIC   | ERJ3EKF6983     |

| R2    | RESISTOR, 49.9K, 1/16W, 0603            | PANASONIC   | ERJ3EKF4992     |

| R3    | RESISTOR, 619K, 1/16W, 0603             | PANASONIC   | ERJ3EKF6193     |

| R4    | RESISTOR, 100K, 1/16W, 0603             | PANASONIC   | ERJ3EKF1003     |

| R5,R6 | RESISTOR, 1.00K, 1/16W, 0603            | PANASONIC   | ERJ3EKF1001     |

| R7    | RESISTOR, 10.0K, 1/16W, 0603            | PANASONIC   | ERJ3EKF1002     |

| R8    | RESISTOR, 4.02K, 1/16W, 0603            | PANASONIC   | ERJ3EKF4021     |

| U1    | IC, BOOST CONTROLLER                    | MICROSEMI   | LX1741          |

| VR1   | ZENER, 24V,225mW, SOT-23                | ON          | BZX84C24LT1     |

Note: The minimum part set for a working power supply consists of: C1, C2, C5, CR1, L1, Q1, R1, R2, R8, U1

PRODUCTION DATA SHEET

# **EVALUATION BOARD (CONTINUED)** CR1 UPS5819 L1 47µH **VBAT** VOUT JB1 **GND** C1 1000pF 50V **GND** VCC SHDN JB2 REF **VADJ** Q2 MMBT3904LT1 ADJ

Figure 8 – LX1741 Boost Evaluation Board Schematic

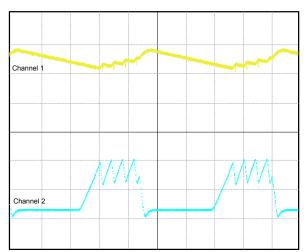

Figure 9 –  $V_{OUT}$  and Inductor Current Waveforms Channel 1:  $V_{OUT}$  (AC coupled; 100 mV/div)

Channel 2: Inductor Current (100mA/div.) Configuration:  $V_{IN} = 1.6V, V_{OUT} = 5.0V, I_{OUT} = 20.0mA$

Figure 10 – Typical V<sub>OUT</sub> versus V<sub>ADJ</sub>

- $0 \sim 0.6$ V : LX1741 uses internal 1.29V reference.

- $0.7V \sim 0.8V$ : transition from internal to external reference.

- 0.9 to 1.6V : LX1741 defaults to external voltage reference.

PRODUCTION DATA SHEET

#### CHARACTERISTIC CURVES

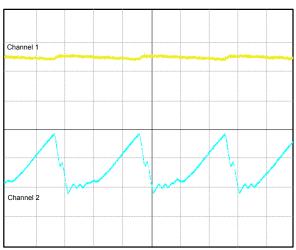

Figure 11 - V<sub>OUT</sub> and Inductor Current Waveforms (mA)

Channel 1: V<sub>OUT</sub> (AC coupled; 100mV/div) Channel 2: Inductor Current (100mA/div.) Configuration:  $V_{\text{IN}} = 3.0\text{V}$ ,  $V_{\text{OUT}} = 17.9\text{V}$ ,  $I_{\text{OUT}} = 11.0\text{mA}$

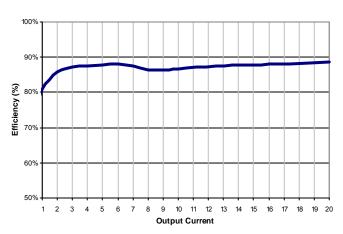

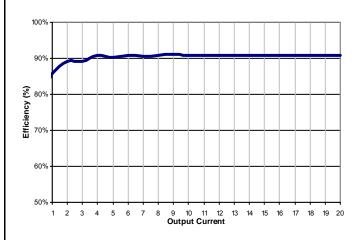

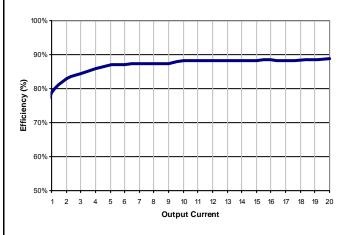

Figure 12 – Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 3.0V$ ,  $V_{OUT} = 17.9V$ ,  $L1 = 47.0\mu H$

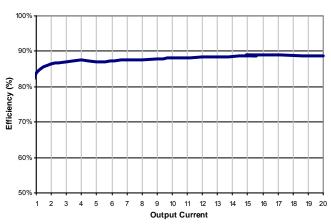

Figure 13 – Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 5.2V$ ,  $V_{OUT} = 17.9V$ ,  $L1 = 94.0 \mu H$

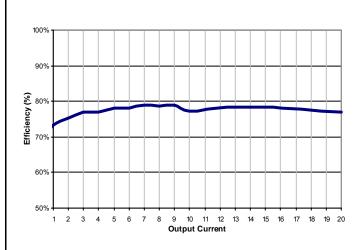

Figure 14 - Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 3.0V$ ,  $V_{OUT} = 10.0V$ ,  $L1 = 47.0\mu H$

PRODUCTION DATA SHEET

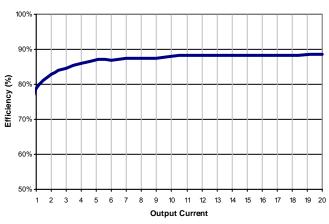

**Figure 15** – Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 1.6V$ ,  $V_{OUT} = 5.0V$ ,  $L1 = 47.0 \mu H$

Figure 16 – Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 3.0V$ ,  $V_{OUT} = 5.0V$ ,  $L1 = 47.0 \mu H$

Figure 17 – Efficiency vs. Output Current (mA) Configuration:  $V_{IN} = 3.0V$ ,  $V_{OUT} = 5.0V$ ,  $L1 = 47.0 \mu H$

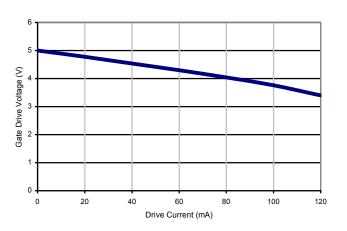

Figure 18 – Gate Drive Voltage vs. Drive Current (mA)

PRODUCTION DATA SHEET

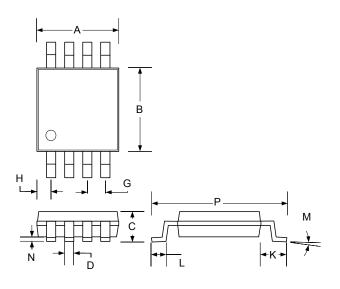

#### **PACKAGE DIMENSIONS**

# **DU** 8-Pin Miniature Shrink Outline Package (MSOP)

| Dim   | MILLIM | ETERS | INC       | HES   |  |

|-------|--------|-------|-----------|-------|--|

| Dilli | MIN    | MAX   | MIN       | MAX   |  |

| Α     | 2.85   | 3.05  | .112      | .120  |  |

| В     | 2.90   | 3.10  | .114      | .122  |  |

| С     | ı      | 1.10  | ı         | 0.043 |  |

| D     | 0.25   | 0.40  | 0.009     | 0.160 |  |

| G     | 0.65   | BSC   | 0.025     | BSC   |  |

| Н     | 0.38   | 0.64  | 0.015     | 0.025 |  |

| J     | 0.13   | 0.18  | 0.005     | 0.007 |  |

| K     | 0.95   | BSC   | 0.037 BSC |       |  |

| L     | 0.40   | 0.70  | 0.016     | 0.027 |  |

| M     | 3°     |       | 3         | o     |  |

| N     | 0.05   | 0.15  | 0.002     | 0.006 |  |

| Р     | 4.75   | 5.05  | 0.187     | 0.198 |  |

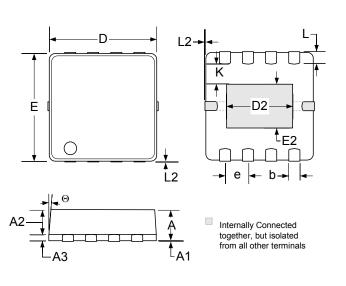

# 8-Pin Plastic MLP-Micro Exposed Pad

| Dim   | MILLIMETERS |      | INCHES    |       |  |

|-------|-------------|------|-----------|-------|--|

| Dilli | MIN         | MAX  | MIN       | MAX   |  |

| Α     | 0.80        | 1.00 | 0.031     | 0.039 |  |

| A1    | 0.00        | 0.05 | 0.000     | 0.002 |  |

| A2    | 0.65        | 0.75 | 0.025     | 0.029 |  |

| A3    | 0.15        | 0.25 | 0.005     | 0.009 |  |

| b     | 0.28        | 0.38 | 0.011     | 0.015 |  |

| D     | 2.90        | 3.10 | 0.114     | 0.122 |  |

| Е     | 2.90        | 3.10 | 0.114     | 0.122 |  |

| е     | 0.65        | BSC  | 0.025 BSC |       |  |

| D2    | 1.52        | 2.08 | 0.060     | 0.082 |  |

| E2    | 1.02        | 1.31 | 0.040     | 0.052 |  |

| K     | 0.20        | *    | 0.008     | *     |  |

| L     | 0.20        | 0.60 | 0.008     | 0.023 |  |

| L2    | 0           | 0.13 | 0         | 0.005 |  |

| Θ     | 0°          | 12°  | 0°        | 12°   |  |

#### Note:

Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

LX1741

# **High Efficiency High Voltage Boost Controller**

PRODUCTION DATA SHEET

NOTES

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.